Polar

3GPP compliant encoding & decoding chain

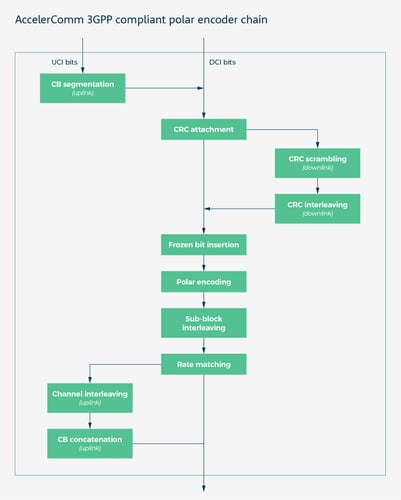

Our patented polar encoding and decoding IP for the 3GPP New Radio uplink and downlink includes the entire processing chain, to provide quick and easy integration and minimize the amount of extra work needed. The polar core uses PC- and CRC-aided SCL polar decoding techniques, in order to achieve compromise-free error correction performance. Our decoding IP has several parameters, which can be adjusted at synthesis-time to scale the parallelism, latency and throughput. The decoder list size can be reduced from the typical list 8, in order to best fit the required application.

Features

- Fully compliant with the 3GPP NR standard for PUCCH, PUSCH, PDCCH and PBCH. Supports the full range of uncoded and encoded block sizes

- Implements the entire Polar encoding and decoding chain in 3GPP TS38.212

- High error correction performance from Polar PC/CRC-aided decoder core

- Tightly integrates the components in the chain to reduce area usage and latency

- Simple interface, quick to integrate.only the number of uncoded bits (A) and encoded bits (E) needs to be input alongside the bits or LLRs

- FPGA support for AMD, Intel and Achronix

- Optimized for ASIC process

- Optimized software solution on Intel Architecture and AVX512 acceleration

- Matlab and C Models available

- Configurable parameters for power and performance optimization

- Scalable design with configurable list size

- Standard AXI interfaces

Functional specifics

| Encoder | Decoder |

|---|---|

| CRC aided SCL encoding | CRC aided SCL decoding |

| Zero padding | Sub block de-interleaving |

| CRC24C attachment | Filler bits insertion/removal |

| CRC scrambling and interleaving | Rate dematching |

| Frozen bit insertion | Channel de-interleaver |

| Sub block interleaving | |

| Rate matching |

Product Codes

| Code | Description | Delivery Type |

|

PD550 |

To enable higher throughput and reduce CPU load. Transport block processing and all code block components are included in the complete Polar 5G NR compliant chain. See Polar decoder chain diagram |

Encrypted RTL or FPGA Netlist |

|

PE550 |

To enable higher throughput and reduce CPU load. Transport block processing and all code block components are included in the complete Polar 5G NR compliant chain. |

Encrypted RTL or FPGA Netlist |

|

PD600 |

Optimized decoder core only for Intel Architecture (IA) and AVX512 co-processor. |

Software binary for IA |

Technical resources

Our technical resources are freely available for anyone to download. Research and innovation form an integral part of our business and we want to share this with you.

Datasheets

Detailed specification sheets for our Polar product, including bloc diagrams, performance graphs and comparison tables.

View DatasheetsWhitepapers

Research, technical leadership and tutorial papers from our CTO on the latest factors influencing the future of Polar standards.

View WhitepapersSoftware

Open source software models and evaluation code for encoder and decoder simulations across our Polar product.

Access SoftwareContact us

We are transforming the next generation of wireless communications with innovative, world-leading IP that delivers ultra-high performance and error resilient 5G. Let’s connect to discuss how our physical layer solutions can help your business thrive today and into the future.

Get in touch

.png?height=500&name=ac-polar-decoder%20(2).png)