PDSCH Encoder

3GPP compliant coding and modulation for Downlink Physical Shared Channels

The Physical Downlink Shared Channel (PDSCH) is used to for downlink data which is shared from the gNB between time and frequency. This channel contains, user equipment control messages, downlink user data and system information. The PDSCH channel needs to be designed with flexibility in mind to support various modulation and coding schemes

AccelerComm’s family of integrated 5G NR channel products, namely PDSCH Encoder and PUSCH Decoder. On this page we detail the PDSCH Encoder which provides Forward Error Correction (FEC) encoding and decoding capabilities along with the complete Quadrature Amplitude Modulation (QAM) modulation and demodulation functionality for downlink data processing in a gNB/base station.

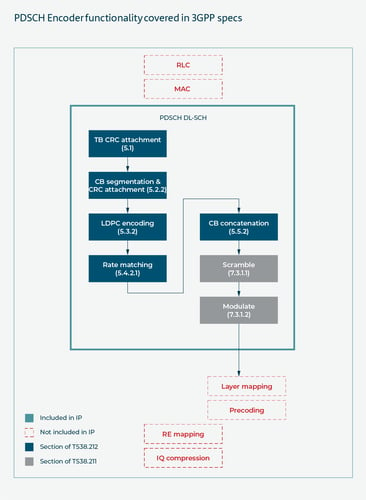

- This IP is implemented as per the latest 3GPP specifications and are compliant with TS 38.211 and 38.212.

- The new QAM modulator functionality complements the existing high performance AccelerComm LDPC and Polar encoder/decoder solutions.

- Like all AccelerComm IP the LDPC and modulator is configurable to several different parallelisms to optimise for SWaP (Size, Weight & Power) of each integration.

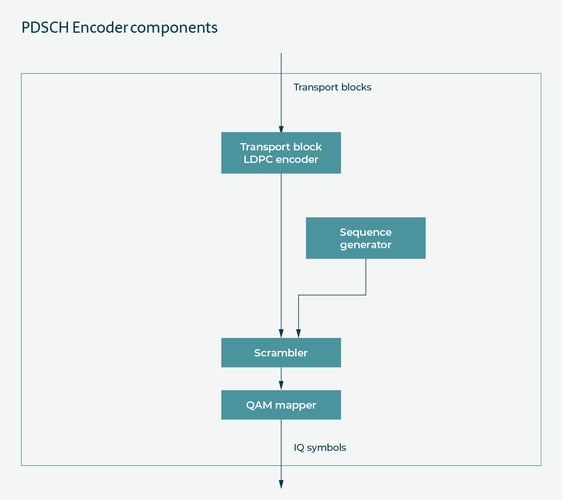

Below is a high-level block diagrams of the functions within these PDSCH encoder IP block:

Features

- The PDSCH Encoder and PUSCH Decoder products simplify the creation of high performance 5G NR implementations.

- PDSCH Encoder features the new QAM mapper and Scrambler functionality. These are integrated with LDPC encoder chain and transport block chain components.

- PDSCH encoder has a configurable IQ parallelism for improved performance per clock.

- The functions included are CRC, Segmentation, LDPC encode, Rate matching, Integrated HARQ, Concatenation, Scrambling and Modulation.

- The tight AccelerComm integration and configurability leads to optimal SWaP solutions.

- This 5G channel IP is delivered as RTL and can be synthesised for FPGA & ASIC target devices.

Benefits

- Complete implementation of the relevant 3GPP standard

- Improved BLER for UCI control data

- Pre integrated with AccelerComm LDPC transport block encoder chains and inherits all the benefits from these

- Single control interface

- Supported across FPGA and ASIC platforms

- Highly configurable for a wide range of base station (gNB) applications

- Configurable to support maximum throughputs and minimum timing requirements for all numerologies

- Very low latency – meets strictest requirements for uRLLC

- Efficient design – saves device area

- Easy to integrate using industry standard AXI interfaces

Functional specifics

The figures below show the functionality within the products, implemented as per the referenced 3GPP specifications.

Further information

PxSCH

For datasheets for our PxSCH product, including bloc diagrams, performance graphs and other KPI comparisons...

contact usLDPC

For more about our configurable LDPC encoder and decoder with multiple algorithm support for optimal BLER performance...

VIEW PRODUCTPolar

For more about our Polar architecture, designed to provide excellent error correction performance within the minimum area...

VIEW PRODUCT

5G PDSCH Encoder & PUSCH Decoder Product Overview

Key features and benefits of our PxSCH product for 3GPP compliant coding and modulation for Psychical Shared Channels.

Download Product Overview NowContact us

We are transforming the next generation of wireless communications with innovative, world-leading IP that delivers ultra-high performance and error resilient 5G. Let’s connect to discuss how our physical layer solutions can help your business thrive today and into the future.

Get in touch