Low Density Parity Check (LDPC)

3GPP Compliant LDPC

3GPP 5G New Radio (NR)

3GPP 5G New Radio (NR) is designed to work across a wide range of use cases delivering unprecedented performance and flexibility from 20Gbps broadband to sub millisecond ultra low latency applications. These requirements present a unique set of challenges for channel coding.

Channel coding or Forward Error Correction (FEC) refers to the process where extra protection bits are added to information bits before transmission. At the receiver, a decoder uses complex algorithms to extract the original information bits from the received data, correcting for errors introduced by interference and fading.

5G NR uses a Low Density Parity Check (LDPC) channel coder for the Physical Uplink and Downlink Shared Channels (PUSCH and PDSCH) over which user data is passed. LDPC is also used in WiFi and satellite broadcast applications, but the variant used in 5G NR is significantly more flexible to support the full range of performance required. It has thousands of possible configurations, as opposed to the handful used in other standards. With the LDPC decoder consuming up to 40% of the resources needed to realise the 5G NR Physical Layer (PHY), decoder performance and efficiency are fundamental to the performance of the overall receiver.

Flexible FEC IP for unique challenges

The AccelerCommTM LDPC decoder product suite has been specifically designed as flexible IP to address the unique challenges of 5G NR across all use cases covered by the current standards, deliver market leading performance and efficiency, and be easily integrated into designs. Key Features Include

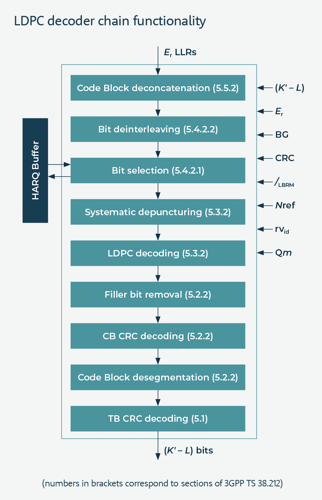

- Complete implementation of the LDPC part of TS 38.212 with optional transport block level processing

- Improved BLER and no error floors – meets strictest requirements for uRLLC

- Proven across muti vendor FPGA and ASIC implementations

- Highly configurable for a wide range of applications

- Design optimised for 5G NR, outperforming generic LDPC decoder solutions

- Configurable to support maximum throughputs and minimum timing requirements for all numerologies and across all HARQ transmissions

- Very low latency – meets requirements for uRLLC

- Efficient design – saves device area

- Low power – half the energy per bit of competitors

- Easy to integrate

5G NR LDPC Product Overview

Key features and benefits of our LDPC product suite for 5G New Radio Applications

Download Now